一、型号说明

纯粹使用cpld的芯片,型号比较多,选型请进。

目前用的比较多的有两个系列:AG1280 和 AGRV2K系列

注:其中的AG1280,处于停产阶段。不再有新的出货,支持也在减少。推荐替换成性价比更高的AGRV2K。AGRV2K是目前主推芯片(以下着重介绍)。

.

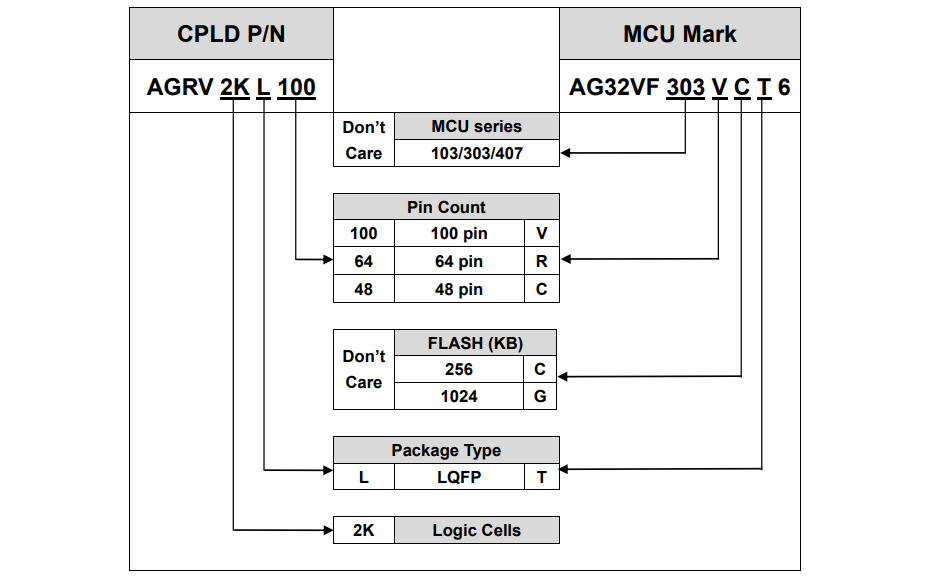

AGRV2K系列就是mcu的AG32系列。两种其实是同一颗料,两种叫法:在cpld市场叫AGRV2K,在MCU市场叫AG32。

关系如下图:

更确切的说:

AG32 = MCU + CPLD,一颗芯片两个内核。mcu核和cpld核可以单独使用,也可以联合使用。

首页提到过AG32的使用方式:

- 只使用 mcu 部分;

- 只使用 cpld 部分;

- 同时使用 mcu 和 cpld(即:mcu 和 cpld 联合编程);

这里所描述的“纯粹cpld”其实就是上述的情况2。

.

二、开发工具、开发流程和烧录工具

开发工具:

纯粹cpld开发中,只需要两个开发软件:Quartus 和 Supra.

两个软件的安装,参考这里的链接。

注:纯粹cpld的开发,不用安装mcu开发的那套软件。

开发流程概述:

1.先使用Supra建立新cpld工程;

首先是创建ve配置文件,然后再创建cpld工程模版,创建的该工程就是Quartus的空工程;

2.用Quartus打开该工程并编写代码、综合;

用Quartus来编写全部的代码,并且编译通过;

3.最后再用Supra来编译出bin;

这里编译出的bin就是要烧录到AGRV2K芯片的bin。

烧录工具:

cpld的烧录,支持两种烧录方式:Supra烧录和downloader烧录。

当supra最终编译完后,会编译出来两个bin:默认的bin、和batch.bin。

默认的bin用supra来烧录,一般用于正常调试;

batch.bin用downloader工具烧录,一般用于生成线上的出厂烧录。downloader烧录支持离线烧录。

对芯片来说,这两个bin在通过两种方式烧录后,效果是完全一样的。有差异的,只是烧录软件和方法。

两种烧录的更详细介绍 点击这里。

.

三、开发说明

quartus下的开发,可以使用verilog语言,也可以使用VHDL语言。两者之间可以相互调用。

凡是Quartus下正常可用的,这里都可以使用,比如,使用altera的IP核。只要确保综合后逻辑单元不超过2K即可(确切讲,是2112个逻辑单元)。

由于只有2K的逻辑单元,不支持cpld的调试。cpld模块写完后,可以使用modelsim来仿真。

纯粹cpld编程时,顶层模块不用再考虑mcu那边的接口,按照正常的设计即可。

.

开发文档:

可以先看2份文档:MANUAL_AGRV2K_3.0.pdf 和 AGRV2K_Rev_3.0.pdf。

1. MANUAL_AGRV2K_3.0.pdf:

该文档为软件开发的基础。

在该文档里会讲述:32/48/64/100Pin的引脚定义、Supra软件安装、新建项目、如何使用时钟(外部和内部)、如何使用内存、编译和烧录。

这个文档应重点看完。

这份文档是cpld开发的基础。后边的开发举例,也是围绕这个文档描述的点展开的。

2. AGRV2K_Rev_3.0.pdf:

该文档为硬件设计文档。

.

四、开发举例

1.建立第一个工程(使用内部晶振,led闪灯);

2.cpld使用adc;

3.待补充;

.